Several CMB-S4 technical subsystems made important advancements during the last few months. The project is entering an exciting development phase.

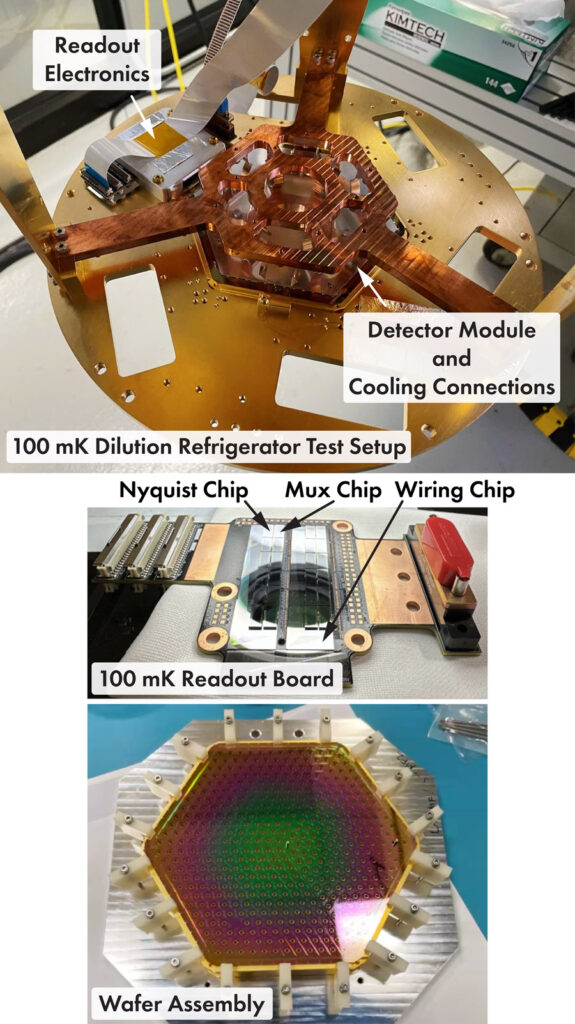

The Module Assembly and Testing team at Fermilab was able to start the first 100 mK test of an integrated detector module including a detector wafer and readout module. Fig. 1 (below) shows the test setup which required a few cool-down iterations before it became fully operational. The arrangement contains a full detector module assembly with interface wafers, horn arrays, and wafer cooling connections. A 100 mK readout enclosure is mounted adjacent to the wafer. Three similar cryostat configurations (at UIUC, SLAC, and FNAL) are now operational and able to test CMB-S4 prototype detector modules.

We can also report notable successes on the detector design side: NIST characterized several LAT-MF prototype single pixel designs plus a CMB-S4 dual-TES bolometer chip. Fig. 2 (below) highlights the NIST single pixel measurement apparatus which utilizes an adiabatic demagnetization refrigerator (ADR). The unique setup allows qualification of passbands, optical efficiency, and polarization responses. Fig. 2 also shows the compact test-board which enables measuring several discrete pixel configurations in a single cool-down. This approach permits rapid development of different design iterations.

![]()

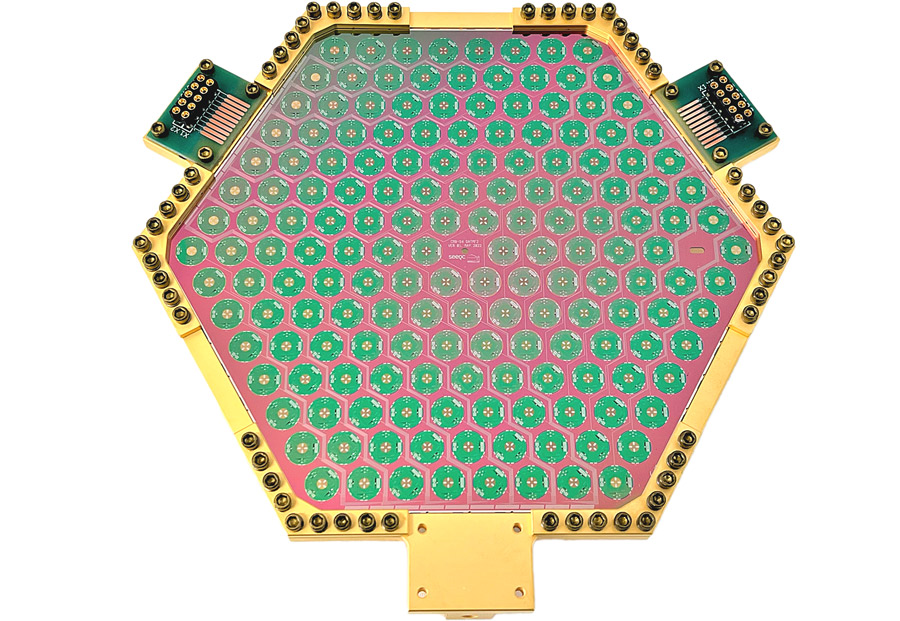

A first SEEQC full SAT-MF wafer prototype test was completed at LBNL (see Fig. 3, below), and dark bolometer data were extracted. Based on these results, SEEQC fabricated a second prototype wafer with further tuned annealing properties to raise the critical temperature of the AlMn transition edge sensors.

The recent Summer Collaboration meeting at SLAC focused on the future publication of a second edition of the CMB-S4 Science Book. SLAC organized an excellent gathering, and the opportunity to discuss topics in person strengthened our collaboration. It was great seeing everyone!

Originally posted in the CMB-S4 July-August 2023 Newsletter